|

|||||||||||||||

|

Loading

FreeRTOS+TCP Simple network interfaces STM32F429Posted by yanvasilij on September 19, 2016 Hello! I am trying to create FreeRTOS+tcp simple network interfaces. I created my own NetworkInterface.c with standard peripheral library and run FreeRTOSIPInit(). Then I tryed ping my board and did'not get ping answer. ETHIRQHandler occures, all program doesn't crash. MCU - STM32F429 compiler - arm-none-eaby-gcc NetworkInterface.c:

~~~ /* Standard includes. */ include

include

include

/* FreeRTOS includes. */ include "FreeRTOS.h"

include "task.h"

include "queue.h"

include "semphr.h"

/* FreeRTOS+TCP includes. */ include "FreeRTOS_IP.h"

include "FreeRTOS_Sockets.h"

include "FreeRTOSIPPrivate.h"

include "NetworkBufferManagement.h"

include "stm32f4x7_eth.h"

include "NetworkInterfaceDefs.h"

/* ST includes. */ include "stm32f4xx.h"

/********************************************************************************** * prototypes *******************************************************************************/ static void prvEMACHandlerTask( void *pvParameters ); /******************************************************************************* * vars *******************************************************************************/ static TaskHandle_t xEMACTaskHandle = NULL; / Ethernet Rx & Tx DMA Descriptors / extern ETHDMADESCTypeDef DMARxDscrTab[ETHRXBUFNB], DMATxDscrTab[ETH_TXBUFNB]; / Ethernet Driver Receive buffers / extern uint8t RxBuff[ETHRXBUFNB][ETHRXBUFSIZE]; /* Ethernet Driver Transmit buffers */ extern uint8t TxBuff[ETHTXBUFNB][ETHTXBUFSIZE]; / Global pointer for last received frame infos */ extern ETHDMARxFrameinfos *DMARXFRAME_infos; /******************************************************************************** * static funs **********************************************************************************/ static void resetPhy (void) { GPIOInitTypeDef gpioInit; unsigned int some; gpioInit.GPIOMode = GPIOModeOUT; gpioInit.GPIOOType = GPIOOTypePP; gpioInit.GPIOPin = GPIOPin12; gpioInit.GPIOPuPd = GPIOPuPdNOPULL; gpioInit.GPIOSpeed = GPIOLowSpeed; GPIOInit(GPIOH, &gpioInit); GPIOWriteBit(GPIOH, GPIOPin12, BitRESET); some=1000000; while (some) some--; GPIOWriteBit(GPIOH, GPIOPin12, Bit_SET); } static void initEthGpios (void) { GPIO_InitTypeDef gpioInit; unsigned int some; } /********************************************************************************** * global **********************************************************************************/ /** * @brief init ehternet controller * * @return / BaseTypet xNetworkInterfaceInitialise( void ) { ETHInitTypeDef ETH_InitStructure; / init randov function */ if( xEMACTaskHandle == NULL ) { RCCAPB2PeriphClockCmd(RCCAPB2PeriphSYSCFG, ENABLE); RCC->AHB1RSTR |= 0x02000000; SYSCFGETHMediaInterfaceConfig(SYSCFGETHMediaInterfaceRMII); } /** * @brief output data processing * * @param pxDescriptor * @param bReleaseAfterSend * * @return */ BaseTypet xNetworkInterfaceOutput( xNetworkBufferDescriptort * const pxDescriptor, BaseType_t bReleaseAfterSend ) { u32 ulTransmitSize = pxDescriptor->xDataLength; } /** * @brief Ethernet Irq */ void ETHIRQHandler( void ) { BaseTypet xHigherPriorityTaskWoken = 0; } define BUFFERSIZE ( ipTOTALETHERNETFRAMESIZE + ipBUFFER_PADDING )

define BUFFERSIZEROUNDEDUP ( ( BUFFERSIZE + 7 ) & ~0x07UL )

static uint8t ucBuffers[ ipconfigNUMNETWORKBUFFERDESCRIPTORS ][ BUFFERSIZEROUNDED_UP ]; /* Static allocation buffers for FreeRTOS+TCP */ void vNetworkInterfaceAllocateRAMToBuffers( NetworkBufferDescriptort pxNetworkBuffers[ ipconfigNUMNETWORKBUFFERDESCRIPTORS ] ) { BaseType_t x; } /** * @brief ethernet driver handling task * * @param pvParameters */ static void prvEMACHandlerTask( void *pvParameters ) { NetworkBufferDescriptort *pxBufferDescriptor; sizet xBytesReceived; IPStackEventt xRxEvent; FrameTypeDef frame; __IO ETHDMADESCTypeDef *DMARxNextDesc; } /********************************************************************************** * eof **********************************************************************************/ ~~~ Creating freertos+tcp task

~~~ /** * @file tcpProcess.cpp * @brief tcp task and etc. * @author * @version * @date 2016-09-16 */ include

/* FreeRTOS includes. */ include

include "task.h"

include "timers.h"

include "queue.h"

include "semphr.h"

/* FreeRTOS+TCP includes. */ include "FreeRTOS_IP.h"

include "FreeRTOS_Sockets.h"

include "FreeRTOS_DHCP.h"

include "stm32f4xx.h"

const uint8t ucIPAddress[ ipIPADDRESSLENGTHBYTES ] = {192, 168, 10, 50}; const uint8t ucNetMask[ ipIPADDRESSLENGTHBYTES ] = { 255, 255, 255, 0 }; const uint8t ucGatewayAddress[ ipIPADDRESSLENGTHBYTES ] = {192, 168, 10, 1}; const uint8t ucDNSServerAddress[ ipIPADDRESSLENGTHBYTES ] = { 208, 67, 222, 222 }; const uint8t ucMACAddress[ ipMACADDRESSLENGTHBYTES ] = { 0x1E, 0x30, 0x6C, 0xA2, 0x45, 0x5C }; /********************************************************************************** * static *******************************************************************************/ static void initRandomFunction (void) { / Enable RNG clock source / RCCAHB2PeriphClockCmd(RCCAHB2Periph_RNG, ENABLE); / RNG Peripheral enable */ RNG_Cmd(ENABLE); } /******************************************************************************** * global ********************************************************************************/ / * @brief random function * * @return */ UBaseTypet uxRand( void ) { const uint32t ulMultiplier = 0x015a4e35UL, ulIncrement = 1UL; static BaseTypet xInitialised = pdFALSE; static UBaseTypet ulNextRand; } /** * @brief start FreeRTOS+TCP */ void initTcpProcess (void) { initRandomFunction(); FreeRTOS_IPInit( ucIPAddress, ucNetMask, ucGatewayAddress, ucDNSServerAddress, ucMACAddress ); } void vApplicationIPNetworkEventHook( eIPCallbackEvent_t eNetworkEvent ) { } void vApplicationPingReplyHook( ePingReplyStatust eStatus, uint16t usIdentifier ) { } /********************************************************************************** * eof **********************************************************************************/ ~~~ FreeRTOS+TCP Simple network interfaces STM32F429Posted by rtel on September 19, 2016 I'm afraid I cannot spend a lot of time reading through a lot of chip specific code as it would only make sense if I also spend a lot of time reading the hardware manual. We either need more information as to how far you get, or you can use the STM32 driver that is already in the FreeRTOS Labs download. With regards to how far you get:

FreeRTOS+TCP Simple network interfaces STM32F429Posted by yanvasilij on September 19, 2016 Thanks for your answer!

FreeRTOS+TCP Simple network interfaces STM32F429Posted by rtel on September 19, 2016 I've never used the TCP stack with co-operative multi-tasking. I'm not sure what the result would be. FreeRTOS+TCP Simple network interfaces STM32F429Posted by yanvasilij on September 19, 2016 Ok. I turned off co-operative multi-tasking (set configUSEPREEMPTION to 1 and configIDLESHOULDYIELD to 0). The problem is still exist. Furthermore I figured out that programm crashed to DefaultHandler after some time. Does I understed correct to port FreeRTOS+TCP and build an application (to check ping only) I need:

? FreeRTOS+TCP Simple network interfaces STM32F429Posted by rtel on September 19, 2016

That is only necessary if you are using BufferAllocation1. BufferAllocation2 is simpler to use, although slower, and prevents you allocating buffers from an ISR. You need to determine which interrupt is calling the default handler in order to start debugging why you end up there. See the "Determining Which Exception Handler is Executing" section on the following page: http://www.freertos.org/Debugging-Hard-Faults-On-Cortex-M-Microcontrollers.html FreeRTOS+TCP Simple network interfaces STM32F429Posted by yanvasilij on September 19, 2016 Yes, I use BufferAllocation_1. I figured out (I used instruction on your link) that HardFault_Handler is occures sometimes (not all time). There is no another tasks in my application except freertos+tcp. FreeRTOS+TCP Simple network interfaces STM32F429Posted by rtel on September 19, 2016 Now you know it is a hard fault you need to find where it is occurring. There is information on that on the same link. Do you have configASSERT() defined, and stack overflow checking set to 2? FreeRTOS+TCP Simple network interfaces STM32F429Posted by yanvasilij on September 19, 2016 I set configASSERT() follows: ~~~ define configASSERT(x) if( ( x ) == 0 ) for(;;)

~~~ configCHECKFORSTACK_OVERFLOW follow: ~~~ define configCHECKFORSTACK_OVERFLOW 2

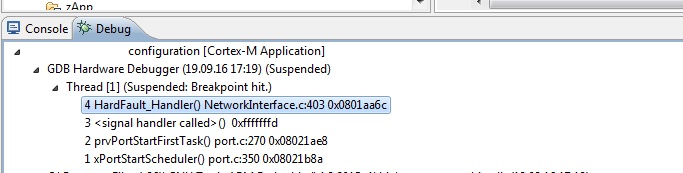

~~~ Declared vApplicationStackOverflowHook: ~~~ void vApplicationStackOverflowHook(void) { while(1); } ~~~ So sheduler start succesfully (I've never stop in configASSERT() ) and I don't get vApplicationStackOverflowHook. When I debug HardFaultHandler I see the follow sequence:

1) prvPortStartFirstTask() called

2) prvPortStartFirstTask() called

3) some strange

FreeRTOS+TCP Simple network interfaces STM32F429Posted by rtel on September 19, 2016

You also need to disable interrupts - otherwise you would only know if you hit the assert if it was the highest priority task that was spinning in the loopl

The call stack doesn't tell you where the fault occurred - to do that you need to pull the program counter off the stack, as described on the previously linked page. FreeRTOS+TCP Simple network interfaces STM32F429Posted by yanvasilij on September 19, 2016 I did the follows: In main: ~~~ int main(void) { uint32t *ACTLR = (uint32t *)0xE000E008; *ACTLR |= 2; //setting the DISDEFWBUF bit (bit 1) ... } ~~~ About configASSERT: ~~~ extern void vAssertCalled (void); define configASSERT(x) if( ( x ) == 0 ) vAssertCalled()

... //somewhere void vAssertCalled (void) { taskDISABLE_INTERRUPTS(); for(;;); } ~~~ There is no change. I still have the same debug sequence when HardFault_Handler occurs. FreeRTOS+TCP Simple network interfaces STM32F429Posted by davedoors on September 19, 2016 but have your found the instruction that was executing when the hard fault happens? FreeRTOS+TCP Simple network interfaces STM32F429Posted by yanvasilij on September 19, 2016 No, I havn't. As Real Time Engineers ltd. sad call stack doesn't tell me where the fault occurred. Setting the DISDEFWBUF bit (bit 1) didn't helped. FreeRTOS+TCP Simple network interfaces STM32F429Posted by rtel on September 19, 2016 The page I linked to in my first (or second?) post that you used to find which handler had been called tells you how to do that though. FreeRTOS+TCP Simple network interfaces STM32F429Posted by yanvasilij on September 19, 2016 I am sorry. I was looking in wrong place. So I declared HardFaultHandler as described [here](http://www.freertos.org/Debugging-Hard-Faults-On-Cortex-M-Microcontrollers.html#armcorteximprecisefaults). When HardFault_Handler occured I looked into pc varible and figured out that it value is 0x0801a9ea. I looked at 0x0801a9ea in disassembly and figured out that instraction that causes fault is: ~~~

/* Set Own bit in Rx descriptors: gives the buffers back to DMA */

for (u32 i=0; i FreeRTOS+TCP Simple network interfaces STM32F429Posted by rtel on September 19, 2016 As a guess I would think DMARxNextDesc had an invalid value when you tried accessing it, so the write to DMARxNextDesc->Status causes a fault. FreeRTOS+TCP Simple network interfaces STM32F429Posted by billskeen68 on October 3, 2016 New to debugging FreeRTOS and trying to follow exactly what to change in code to be able to get a precise hard fault PC register address to debug my application. I've reviewed this thread, the link from Real Time Engineers and several others, like: http://www.freertos.org/Debugging-Hard-Faults-On-Cortex-M-Microcontrollers.html and https://blog.frankvh.com/2011/12/07/cortex-m3-m4-hard-fault-handler/ Could someone help out a noob and point me to something specific please? Thanks in advance. FreeRTOS+TCP Simple network interfaces STM32F429Posted by rtel on October 4, 2016 The link you posted contains source code to do this, so I'm not sure what other specific information can be provided. Perhaps if you could show/explain what you have tried and why it didn't work we could provide some suggestions. FreeRTOS+TCP Simple network interfaces STM32F429Posted by billskeen68 on October 4, 2016 I am using the FreeRTOS/Particle/Redbear Duo version of the firmware from: https://github.com/redbear/firmware The bug I am trying to find is with my code calling TCPClient.write that is failing randomly. I do a serial print of the up to 900 byte message just before the write and I can see no problems with it. Sometimes it fails immediately after startup, sometimes days or weeks later. When it does fail, I get a HardFault code 1 ( SOS blinks, then 1 blink, repeat). I have compiled a debug version using Particle/RedBear make files and I have a breakpoint on the prvGetRegistersFromStack function in the corehalstm32f2xx.c file. This is the file/function RedBear support told me to put the breakpoint. When the breakpoint is hit, I examine the pc register and it is pointing to the HardFault_Handler: Breakpoint 1, HardFaultHandler () at src/stm32f2xx/corehalstm32f2xx.c:112 112 __asm volatile (gdb) info registers r0 0x0 0 r1 0x0 0 r2 0x2 2 r3 0x20020000 537001984 r4 0x20000dfc 536874492 r5 0x20000dfc 536874492 r6 0x8077da0 134708640 r7 0x20 32 r8 0xa5a5a5a5 -1515870811 r9 0xa5a5a5a5 -1515870811 r10 0xa5a5a5a5 -1515870811 r11 0xa5a5a5a5 -1515870811 r12 0xccccccc 214748364 sp 0x2001ffe0 0x2001ffe0 lr 0xfffffffd -3 pc 0x80533be 0x80533be <HardFaultHandler> xPSR 0x61000003 1627389955 Not sure what to do from here. That was the reason for the precise hardfault question. FreeRTOS+TCP Simple network interfaces STM32F429Posted by rtel on October 4, 2016 Have you followed the instructions in the "Handling Imprecise Faults" section of the page previously linked (setting bit 1 of the ACTLR register)? FreeRTOS+TCP Simple network interfaces STM32F429Posted by billskeen68 on October 4, 2016 That is the part I am not sure of where/what to do. Does this code go in core_hal.c, somewhere near/before the vTaskStartScheduler();? int main(void) { initmallocmutex(); xTaskCreate( applicationtaskstart, "appthread", APPLICATIONSTACKSIZE/sizeof( portSTACKTYPE ), NULL, 2, &appthreadhandle); } How do I determine if I need configAssert and where does it go? Sorry to be so dumb here, but learning as I go. FreeRTOS+TCP Simple network interfaces STM32F429Posted by davedoors on October 4, 2016 in main: ~~~ uint32t * ACTLR = ((uint32t*)0xE000E008) uint32_t temp; temp = *ACTLR; temp |= 0x02; *ACTLR = temp; // bit now set ~~~ FreeRTOS+TCP Simple network interfaces STM32F429Posted by billskeen68 on October 4, 2016 Okay, I added the 2 lines of code to the core_hal.c main function, recompiled debug version and now waiting for breakpoint hit. Interesting to note that this slowed down BLE device detection considerably. What used to take less than 30 seconds at startup now takes 4-5 minutes. FreeRTOS+TCP Simple network interfaces STM32F429Posted by edwards3 on October 5, 2016 from the FreeRTOS page "turning off write buffering by setting the DISDEFWBUF bit (bit 1) in the Auxiliary Control Register (or ACTLR) will result in the imprecise fault becoming a precise fault, which makes the fault easier to debug, albeit at the cost of slower program execution." FreeRTOS+TCP Simple network interfaces STM32F429Posted by billskeen68 on October 5, 2016 Thanks MEdwards. I did read that. I just was not expecting 10x slower. Now that I have made that change, I have not had a hardfault since. Not sure what to do now, so going back to board mfg for suggestions. Thank all for the help.

Copyright (C) Amazon Web Services, Inc. or its affiliates. All rights reserved.

|

|||||||||||||||

NXP tweet showing LPC5500 (ARMv8-M Cortex-M33) running FreeRTOS.

Meet Richard Barry and learn about running FreeRTOS on RISC-V at FOSDEM 2019

Version 10.1.1 of the FreeRTOS kernel is available for immediate download. MIT licensed.

View a recording of the "OTA Update Security and Reliability" webinar, presented by TI and AWS.

FreeRTOS and other embedded software careers at AWS.